The ever-shrinking world of electronics just got smaller following the first demonstration of digital logic circuits made from carbon nanotubes. Cees Dekker and team at Delft University of Technology in the Netherlands used different combinations of 'nanotube transistors' to create several devices, including a voltage inverter and a NOR gate. As conventional silicon microelectronics approaches its fundamental size limit, Dekker and colleagues believe that their devices - which work at room temperature - are an important step towards nano-electronics (A Bachtold et al 2001 Science to appear).

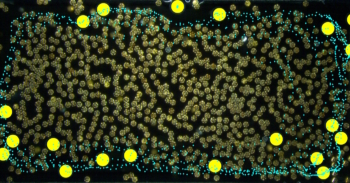

Carbon nanotubes are rolled-up sheets of graphite about a nanometre in diameter. They have previously been used to make a variety of electronic components, including diodes and field-effect transistors (FETs). A FET can be made from a nanotube by attaching gate, source and drain electrodes to it. Dekker’s group has now placed several of these FETs on a single silicon chip to form different circuits.

Their simple inverter device consists of a nanotube FET and a large bias resistance: it converts a high input voltage to a low one – that is, “one” to “zero” – and vice versa. By adding an extra FET in parallel, the researchers made a NOR gate. This device needs two “zero” inputs to give a “one” output, or two “ones” to give a “zero”.

Any of the standard logic gates – AND, OR, NAND and so on – can be created using different arrangements of these FETs. The team also created a ‘static random access memory’ and an oscillator that generates an ac signal. The devices have gains of a factor of ten.

The Delft group used electron beam lithography to deposit aluminium gate electrodes onto a silicon wafer, placed the nanotubes on top, and added gold electrodes by an evaporation technique. Despite their achievement, Dekker and colleagues admit that there are still challenges to overcome, such as the difficulty in positioning the nanotubes accurately on the wafer. But the team hopes that emerging techniques – including a way to grow nanotubes directly onto the chip – may solve this problem.